QVGA Display with Ethernet Interface

As part of my bachelor thesis, I designed an ethernet interface for data communication between two devices. The design goal of this interface was minimal latency which is very important for certain applications.

The idea of this design started with a project that was worked on at the 'Eindhoven University of Technology'. This project was set up to eliminate atmospheric vibrations on telescope images. The main idea was to build a matrix of mirrors, which would separately pivot in all directions to compensate for the vibrations picked up by the telescope. To control these mirrors a fast no-nonsense communication protocol was needed. The speed of a standard ethernet interface was not sufficient, due to the fact that they are mostly implemented in software. The idea came to develop an ethernet interface with only UDP/IP capacities in hardware.

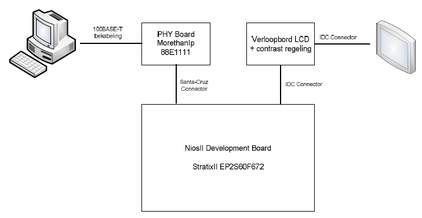

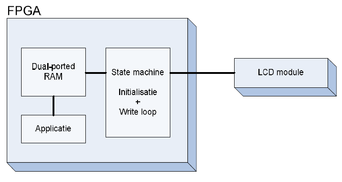

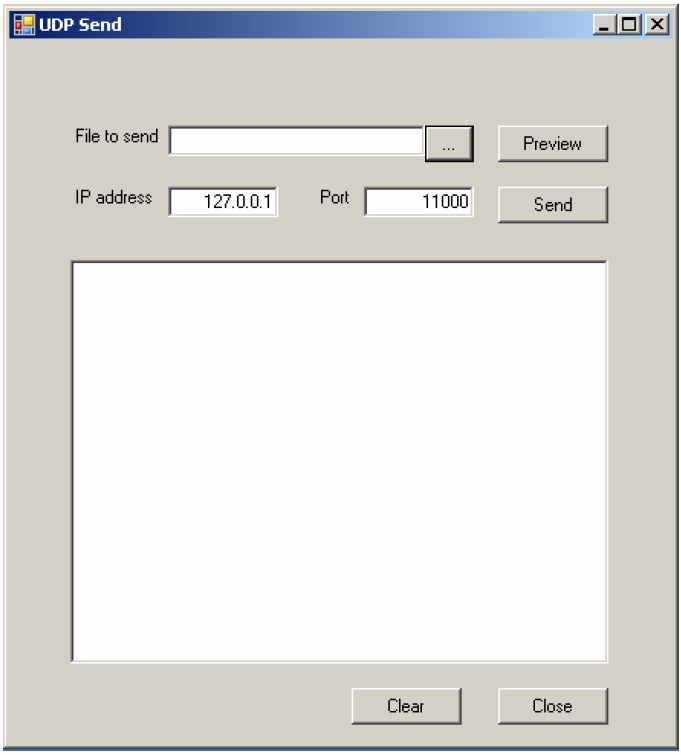

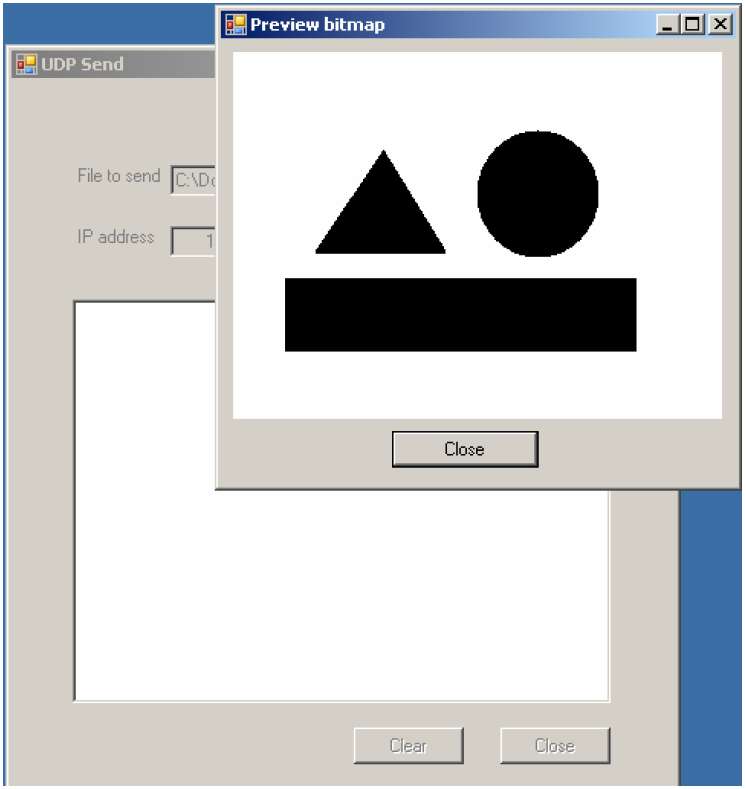

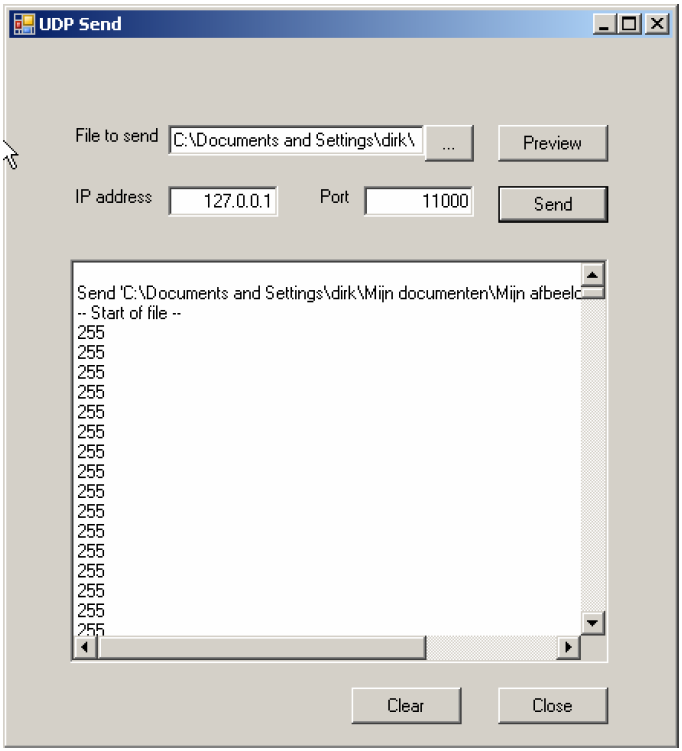

To realize this interface a Stratix II FPGA from Altera is used with external only a PHY-chip accompanied by the necessary magnetics. To visualize the data transfers through the interface a small PC-application is written in Visual Basic. This application is able to open a bitmap-file en send it by means of UDP/IP communication. At the receiver side a QVGA display is attached to the FPGA to visualize the receiving of the bitmap.

The project is written in VHDL on behavioral level, and build with schematic-entry on structural level.

The idea of this design started with a project that was worked on at the 'Eindhoven University of Technology'. This project was set up to eliminate atmospheric vibrations on telescope images. The main idea was to build a matrix of mirrors, which would separately pivot in all directions to compensate for the vibrations picked up by the telescope. To control these mirrors a fast no-nonsense communication protocol was needed. The speed of a standard ethernet interface was not sufficient, due to the fact that they are mostly implemented in software. The idea came to develop an ethernet interface with only UDP/IP capacities in hardware.

To realize this interface a Stratix II FPGA from Altera is used with external only a PHY-chip accompanied by the necessary magnetics. To visualize the data transfers through the interface a small PC-application is written in Visual Basic. This application is able to open a bitmap-file en send it by means of UDP/IP communication. At the receiver side a QVGA display is attached to the FPGA to visualize the receiving of the bitmap.

The project is written in VHDL on behavioral level, and build with schematic-entry on structural level.

Project Overview

Hier klikken om te bewerken.

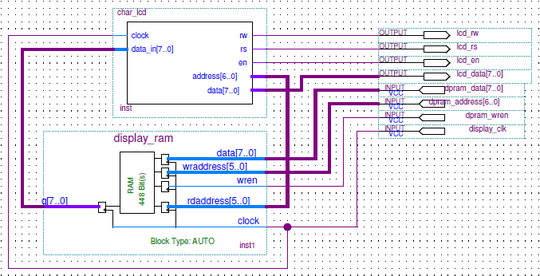

QVGA Display Interface

Hier klikken om te bewerken.

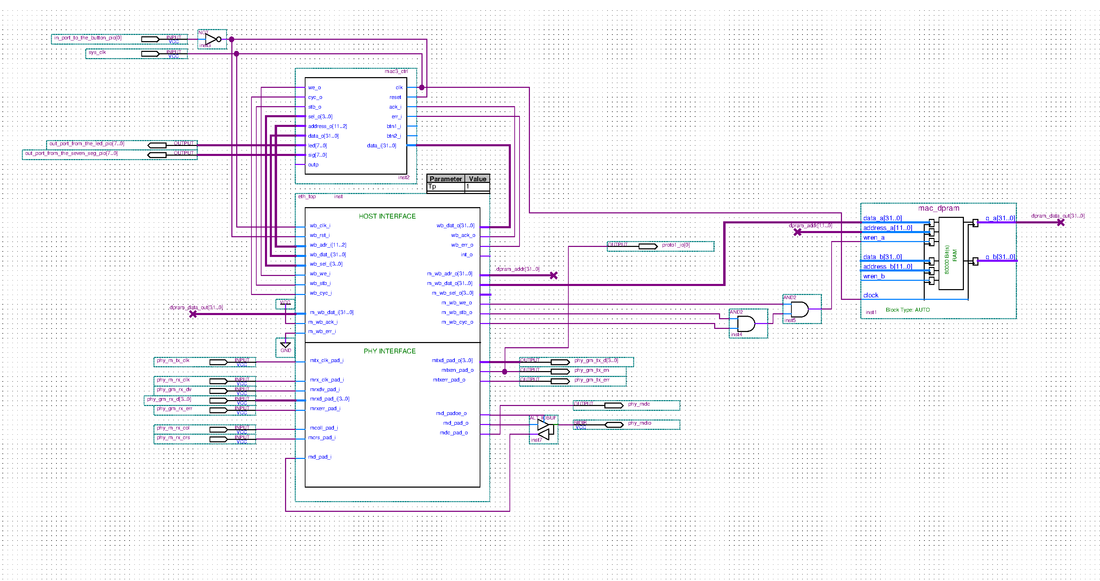

Top Level Design with Soft-core

Hier klikken om te bewerken.